mirror of

https://github.com/enjoy-digital/litex.git

synced 2025-01-04 09:52:26 -05:00

README: update example projects built with the tools, remove 2020.04 note.

This commit is contained in:

parent

3e115a0ecb

commit

052a76f253

1 changed files with 7 additions and 5 deletions

12

README.md

12

README.md

|

|

@ -6,8 +6,6 @@

|

||||||

[](https://github.com/enjoy-digital/litex/actions)

|

[](https://github.com/enjoy-digital/litex/actions)

|

||||||

|

|

||||||

|

|

||||||

> **Note:** In release 2020.04, LiteX switched to Python modules instead of Git submodules. Existing users will have to reinstall LiteX following the [installation guide](https://github.com/enjoy-digital/litex/wiki/Installation#litex-installation-guide).

|

|

||||||

|

|

||||||

# Welcome to LiteX!

|

# Welcome to LiteX!

|

||||||

|

|

||||||

LiteX is a Migen/MiSoC based Core/SoC builder that provides the infrastructure to easily create Cores/SoCs (with or without CPU).

|

LiteX is a Migen/MiSoC based Core/SoC builder that provides the infrastructure to easily create Cores/SoCs (with or without CPU).

|

||||||

|

|

@ -53,10 +51,14 @@ LiteX already supports various softcores CPUs: VexRiscv, Rocket, LM32, Mor1kx, P

|

||||||

| [LiteVideo](http://github.com/enjoy-digital/litevideo) | [](https://github.com/enjoy-digital/litevideo/actions) | VGA, DVI, HDMI |

|

| [LiteVideo](http://github.com/enjoy-digital/litevideo) | [](https://github.com/enjoy-digital/litevideo/actions) | VGA, DVI, HDMI |

|

||||||

| [LiteScope](http://github.com/enjoy-digital/litescope) | [](https://github.com/enjoy-digital/litescope/actions) | Logic analyzer |

|

| [LiteScope](http://github.com/enjoy-digital/litescope) | [](https://github.com/enjoy-digital/litescope/actions) | Logic analyzer |

|

||||||

|

|

||||||

Combining LiteX with the ecosystem of cores allows the creation of complex SoCs such as the one below

|

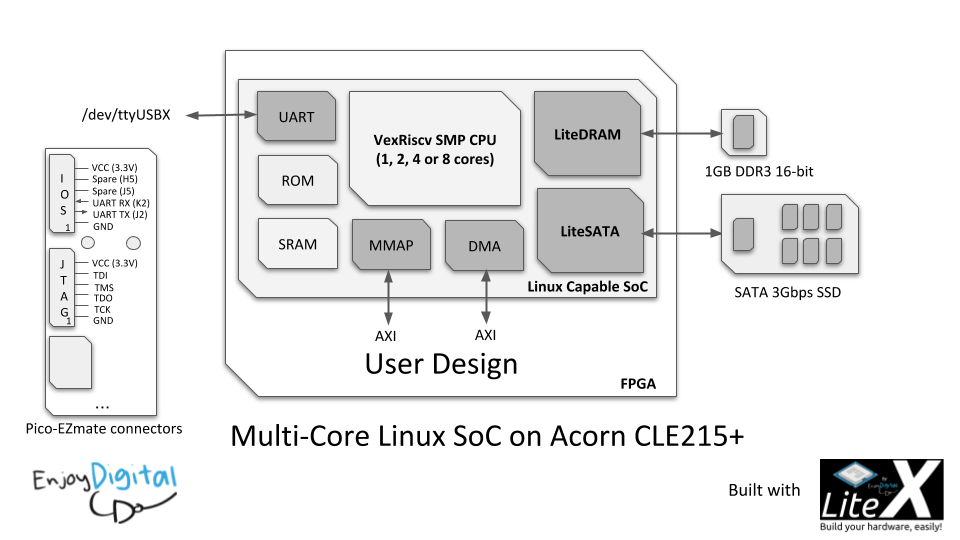

By combining LiteX with the ecosystem of cores, creating complex SoCs becomes easier than with traditional tools while providing better portability and flexibility. Here are some projects created recently with the tools:

|

||||||

created for the NeTV2 board to do HDMI capture/playback over PCIe:

|

|

||||||

|

|

||||||

<p align="center"><img width="800" src="https://raw.githubusercontent.com/enjoy-digital/netv2/master/doc/architecture.png"></p>

|

A Multi-core Linux Capable SoC based on VexRiscv-SMP CPU, LiteDRAM, LiteSATA and integrated with LiteX:

|

||||||

|

For more info, have a look at [Linux-on-LiteX-Vexriscv](https://github.com/litex-hub/linux-on-litex-vexriscv) project and try running Linux on your FPGA board!

|

||||||

|

|

||||||

|

A custom PCIe SDI Capture/Playback board built around LitePCIe and integrated with LiteX, allowing full control of the SDI flow and very low latency.

|

||||||

|

|

||||||

|

To discover more products/projects built with LiteX, visit the [projects page](https://github.com/enjoy-digital/litex/wiki/Projects) on the Wiki.

|

||||||

|

|

||||||

# Papers, Presentations, Tutorials, Links

|

# Papers, Presentations, Tutorials, Links

|

||||||

**FPGA lessons/tutorials:**

|

**FPGA lessons/tutorials:**

|

||||||

|

|

|

||||||

Loading…

Reference in a new issue