README.md: Rewrite Welcome section and update copyright.

This commit is contained in:

parent

9a51dfb50e

commit

2b49430f2c

65

README.md

65

README.md

|

|

@ -1,22 +1,56 @@

|

||||||

<p align="center"><img src="https://raw.githubusercontent.com/enjoy-digital/litex/master/doc/litex.png"></p>

|

<p align="center"><img src="https://raw.githubusercontent.com/enjoy-digital/litex/master/doc/litex.png"></p>

|

||||||

|

|

||||||

```

|

```

|

||||||

Copyright 2012-2021 / Enjoy-Digital

|

Copyright 2012-2021 / Enjoy-Digital & LiteX developers

|

||||||

```

|

```

|

||||||

[](https://github.com/enjoy-digital/litex/actions)

|

[](https://github.com/enjoy-digital/litex/actions)

|

||||||

|

|

||||||

|

|

||||||

# Welcome to LiteX!

|

# Welcome to LiteX!

|

||||||

|

|

||||||

LiteX is a Migen/MiSoC based Core/SoC builder that provides the infrastructure to easily create Cores/SoCs (with or without CPU).

|

|

||||||

The common components of a SoC are provided directly: Buses and Streams (Wishbone, AXI, Avalon-ST), Interconnect, Common cores (RAM, ROM, Timer, UART, etc...), CPU wrappers/integration, etc... and SoC creation capabilities can be greatly extended with the ecosystem of LiteX cores (DRAM, PCIe, Ethernet, SATA, etc...) that can be integrated/simulated/build easily with LiteX. It also provides build backends for open-source and vendors toolchains.

|

|

||||||

|

|

||||||

Think of Migen as a toolbox to create FPGA designs in Python and LiteX as a

|

The LiteX framework provides a convenient and efficient infrastructure to create FPGA Cores/SoCs, to explore various digital design architectures and create [full FPGA based systems](https://github.com/enjoy-digital/litex/wiki/Projects).

|

||||||

SoC builder to create/develop/debug FPGA SoCs in Python.

|

|

||||||

|

|

||||||

**Want to get started and/or looking for documentation? Make sure to visit the [Wiki](https://github.com/enjoy-digital/litex/wiki)!**

|

**Want to get started and/or looking for documentation? Make sure to visit the [Wiki](https://github.com/enjoy-digital/litex/wiki)!**

|

||||||

|

|

||||||

**A question or want to get in touch? Our IRC channel is [#litex at irc.libera.chat]**

|

**A question or want to get in touch? Our IRC channel is [#litex at irc.libera.chat]**.

|

||||||

|

|

||||||

|

LiteX provides all the common components required to easily create an FPGA Core/SoC:

|

||||||

|

- :heavy_check_mark: Buses and Streams (Wishbone, AXI, Avalon-ST) and their interconnect.

|

||||||

|

- :heavy_check_mark: Simple cores: RAM, ROM, Timer, UART, JTAG, etc….

|

||||||

|

- :heavy_check_mark: Complex cores through the ecosystem of cores: [LiteDRAM](https://github.com/enjoy-digital/litedram), [LitePCIe](https://github.com/enjoy-digital/litepcie), [LiteEth](https://github.com/enjoy-digital/liteeth), [LiteSATA](https://github.com/enjoy-digital/litesata), etc...

|

||||||

|

- :heavy_check_mark: Various CPUs & ISAs: RISC-V, OpenRISC, LM32, Zynq, X86 (through a PCIe), etc...

|

||||||

|

- :heavy_check_mark: Mixed languages support with VHDL/Verilog/(n)Migen/Spinal-HDL/etc... integration capabilities.

|

||||||

|

- :heavy_check_mark: Powerful debug infractrusture through the various [bridges](https://github.com/enjoy-digital/litex/wiki/Use-Host-Bridge-to-control-debug-a-SoC) and [Litescope](https://github.com/enjoy-digital/litescope).

|

||||||

|

- :heavy_check_mark: Direct/Fast simulation through [Verilator](https://www.veripool.org/verilator/).

|

||||||

|

- :heavy_check_mark: Build backends for open-source and vendors toolchains.

|

||||||

|

- :heavy_check_mark: And a lot more... :)

|

||||||

|

|

||||||

|

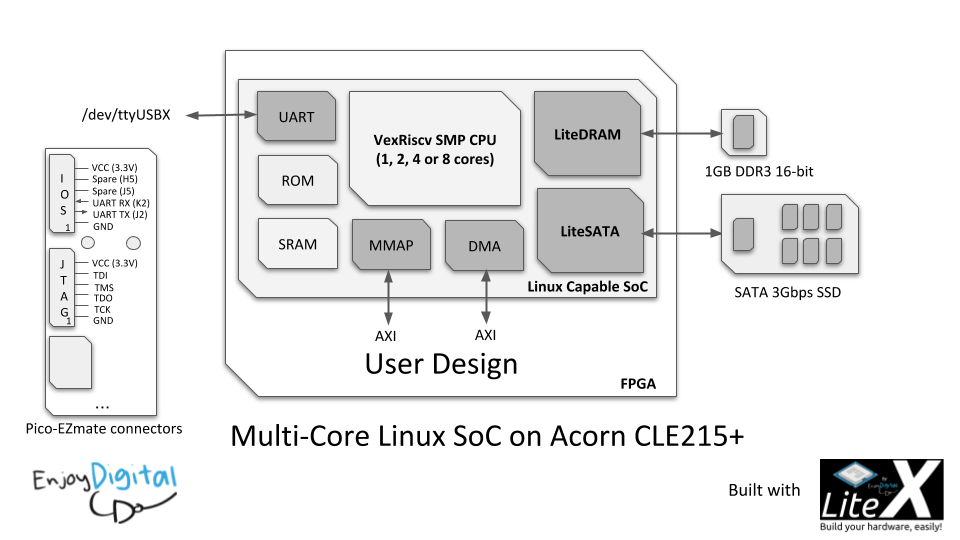

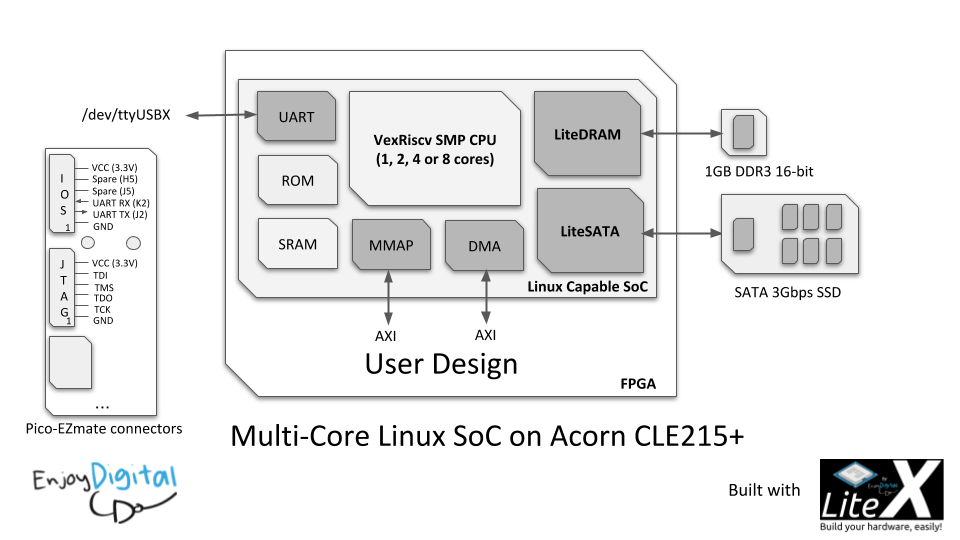

By combining LiteX with the ecosystem of cores, creating complex SoCs becomes a lot easier than with traditional approaches while providing better portability and flexibility: Here is for example a Multi-core Linux Capable SoC based on VexRiscv-SMP CPU, LiteDRAM, LiteSATA built and integrated with LiteX, running on a cheap repurposed [Acorn CLE215+ Mining Board](https://github.com/enjoy-digital/litex/wiki/Use-LiteX-on-the-Acorn-CLE-215):

|

||||||

|

|

||||||

|

For more info, have a look at [Linux-on-LiteX-Vexriscv](https://github.com/litex-hub/linux-on-litex-vexriscv) project and try running Linux on your FPGA board!

|

||||||

|

|

||||||

|

LiteX's digital logic is currently described with [Migen](https://github.com/m-labs/migen) which does not prevent users to create mixed language projects:

|

||||||

|

- It's very common and easy to integrate VHDL/Verilog/SystemVerilog/nMigen/Spinal-HDL code in LiteX!

|

||||||

|

- It's also very common to do the opposite and generate the LiteX design as a verilog file and integrate it in a traditional flow.

|

||||||

|

|

||||||

|

|

||||||

|

LiteX was initially developed by [Enjoy-Digital](http://enjoy-digital.fr/) to create projects for clients (and we are still using it for that :)) and trying to take the different clients' requirements/needs consideration made, we think, the framework very flexible:

|

||||||

|

- Some users only want to use it to easily interconnect their existing VHDL/Verilog/SV cores.

|

||||||

|

- Some users are only interested to reuse the PCIe/Ethernet/SATA/etc cores as regular core and just integrate them in their traditional flow.

|

||||||

|

- Some users with a hardware background start with the above approaches and then switch later to the full Python flow since find it more efficient.

|

||||||

|

- Some users with a software background and fluent with Python start playing with FPGAs while they would probably never touch FPGA otherwise :)

|

||||||

|

- Etc...

|

||||||

|

|

||||||

|

We are well aware that everyone has a different background, so it's up to you to pick the right approach with LiteX that will be convenient for you!

|

||||||

|

|

||||||

|

To get started we encourage you to read the [wiki](https://github.com/enjoy-digital/litex/wiki).

|

||||||

|

|

||||||

|

You already have a FPGA board(s)? Visit [LiteX-Boards](https://github.com/litex-hub/litex-boards) to see if your board(s) is already supported!

|

||||||

|

|

||||||

|

The framework is also far from perfect and we'll be happy to have your [feedback or/and contributions](https://github.com/enjoy-digital/litex/wiki/Feedback-Contribution-Support).

|

||||||

|

|

||||||

|

Have fun! :wink:

|

||||||

|

|

||||||

# Typical LiteX design flow:

|

# Typical LiteX design flow:

|

||||||

```

|

```

|

||||||

|

|

@ -53,13 +87,14 @@ LiteX already supports various softcores CPUs: VexRiscv, Rocket, LM32, Mor1kx, P

|

||||||

| [LiteVideo](http://github.com/enjoy-digital/litevideo) | [](https://github.com/enjoy-digital/litevideo/actions) | VGA, DVI, HDMI |

|

| [LiteVideo](http://github.com/enjoy-digital/litevideo) | [](https://github.com/enjoy-digital/litevideo/actions) | VGA, DVI, HDMI |

|

||||||

| [LiteScope](http://github.com/enjoy-digital/litescope) | [](https://github.com/enjoy-digital/litescope/actions) | Logic analyzer |

|

| [LiteScope](http://github.com/enjoy-digital/litescope) | [](https://github.com/enjoy-digital/litescope/actions) | Logic analyzer |

|

||||||

|

|

||||||

By combining LiteX with the ecosystem of cores, creating complex SoCs becomes easier than with traditional tools while providing better portability and flexibility. Here are some projects created recently with the tools:

|

# Examples of designs built with LiteX:

|

||||||

|

Custom PCIe SDI Capture/Playback board built around LitePCIe and integrated with LiteX, allowing full control of the SDI flow and very low latency.

|

||||||

A Multi-core Linux Capable SoC based on VexRiscv-SMP CPU, LiteDRAM, LiteSATA and integrated with LiteX:

|

|

||||||

For more info, have a look at [Linux-on-LiteX-Vexriscv](https://github.com/litex-hub/linux-on-litex-vexriscv) project and try running Linux on your FPGA board!

|

|

||||||

|

|

||||||

A custom PCIe SDI Capture/Playback board built around LitePCIe and integrated with LiteX, allowing full control of the SDI flow and very low latency.

|

|

||||||

|

|

||||||

|

Alternative firmware/gateware for the SDS1104X-E Scope:

|

||||||

|

|

||||||

|

HBM2 test infrastructure on Forest Kitten 33:

|

||||||

|

|

||||||

|

|

||||||

To discover more products/projects built with LiteX, visit the [projects page](https://github.com/enjoy-digital/litex/wiki/Projects) on the Wiki.

|

To discover more products/projects built with LiteX, visit the [projects page](https://github.com/enjoy-digital/litex/wiki/Projects) on the Wiki.

|

||||||

|

|

||||||

# Papers, Presentations, Tutorials, Links

|

# Papers, Presentations, Tutorials, Links

|

||||||

|

|

@ -151,11 +186,7 @@ $ lxsim --cpu-type=vexriscv

|

||||||

|

|

||||||

<p align="center"><img src="https://raw.githubusercontent.com/enjoy-digital/litex/master/doc/litex-hub.png" width="400"></p>

|

<p align="center"><img src="https://raw.githubusercontent.com/enjoy-digital/litex/master/doc/litex-hub.png" width="400"></p>

|

||||||

|

|

||||||

LiteX has been initially developed by EnjoyDigital to create custom SoCs/Systems for our clients

|

Over the years a friendly community has grown around LiteX and the ecosystem of cores. Feedbacks and contributions have already greatly improved the project, EnjoyDigital still leads the development but it is now a community project and collaborative projects created around/with LiteX can be found at https://github.com/litex-hub.

|

||||||

(and we are still using it for that purpose :)); but over the years a friendly community has grown

|

|

||||||

around LiteX and the ecosystem of cores. Feedbacks and contributions have already greatly improved

|

|

||||||

the project, EnjoyDigital still leads the development but it is now a community project and collaborative

|

|

||||||

projects created around/with LiteX can be found at https://github.com/litex-hub.

|

|

||||||

|

|

||||||

# Contact

|

# Contact

|

||||||

E-mail: florent@enjoy-digital.fr

|

E-mail: florent@enjoy-digital.fr

|

||||||

|

|

|

||||||

Loading…

Reference in New Issue