| doc | ||

| litex | ||

| test | ||

| .gitignore | ||

| .travis.yml | ||

| CHANGES | ||

| CONTRIBUTORS | ||

| LICENSE | ||

| litex_setup.py | ||

| MANIFEST.in | ||

| README.md | ||

| setup.py | ||

Copyright 2012-2020 / Enjoy-Digital

Note: In release 2020.04, LiteX switched to Python modules instead of Git submodules. Existing users will have to reinstall LiteX following the installation guide.

Welcome to LiteX!

LiteX is a Migen/MiSoC based Core/SoC builder that provides the infrastructure to easily create Cores/SoCs (with or without CPU). The common components of a SoC are provided directly: Buses and Streams (Wishbone, AXI, Avalon-ST), Interconnect, Common cores (RAM, ROM, Timer, UART, etc...), CPU wrappers/integration, etc... and SoC creation capabilities can be greatly extended with the ecosystem of LiteX cores (DRAM, PCIe, Ethernet, SATA, etc...) that can be integrated/simulated/build easily with LiteX. It also provides build backends for open-source and vendors toolchains.

Think of Migen as a toolbox to create FPGA designs in Python and LiteX as a SoC builder to create/develop/debug FPGA SoCs in Python.

A question or want to get in touch? Our IRC channel is #litex at freenode.net

Typical LiteX design flow:

+---------------+

|FPGA toolchains|

+----^-----+----+

| |

+--+-----v--+

+-------+ | |

| Migen +--------> |

+-------+ | | Your design

| LiteX +---> ready to be used!

| |

+----------------------+ | |

|LiteX Cores Ecosystem +--> |

+----------------------+ +-^-------^-+

(Eth, SATA, DRAM, USB, | |

PCIe, Video, etc...) + +

board target

file file

LiteX already supports various softcores CPUs: VexRiscv, Rocket, LM32, Mor1kx, PicoRV32 and is compatible with the LiteX's Cores Ecosystem:

| Name | Build Status | Description |

|---|---|---|

| LiteDRAM | DRAM | |

| LiteEth | Ethernet | |

| LitePCIe | PCIe | |

| LiteSATA | SATA | |

| LiteSDCard | SD card | |

| LiteICLink | Inter-Chip communication | |

| LiteJESD204B | JESD204B | |

| LiteVideo | VGA, DVI, HDMI | |

| LiteScope | Logic analyzer |

Combining LiteX with the ecosystem of cores allows the creation of complex SoCs such as the one below created for the NeTV2 board to do HDMI capture/playback over PCIe:

Papers, Presentations, Tutorials, Links

FPGA lessons/tutorials:

Migen tutorial:

OSDA 2019 paper/slides:

Linux on LiteX-Vexriscv:

RISC-V Getting Started Guide:

LiteX vs. Vivado First Impressions:

35C3 - Snakes and Rabbits - How CCC shaped an open hardware success:

Tim has to many projects - LatchUp Edition: https://www.youtube.com/watch?v=v7WrTmexod0

Sub-packages

litex.gen Provides specific or experimental modules to generate HDL that are not integrated in Migen.

litex.build: Provides tools to build FPGA bitstreams (interface to vendor toolchains) and to simulate HDL code or full SoCs.

litex.soc: Provides definitions/modules to build cores (bus, bank, flow), cores and tools to build a SoC from such cores.

litex.boards: Provides platforms and targets for the supported boards. All Migen's platforms can also be used in LiteX. The boards present in the LiteX repository are the official ones that are used for development/CI. More boards are available at: https://github.com/litex-hub/litex-boards

Quick start guide

- Install Python 3.6+ and FPGA vendor's development tools and/or Verilator.

- Install Migen/LiteX and the LiteX's cores:

$ wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

$ chmod +x litex_setup.py

$ ./litex_setup.py init install --user (--user to install to user directory)

Later, if you need to update all repositories:

$ ./litex_setup.py update

Note: On MacOS, make sure you have HomeBrew installed. Then do,

brew install wget.

Note: On Windows, it's possible you'll have to set

SHELLenvironment variable toSHELL=cmd.exe.

- Install a RISC-V toolchain (Only if you want to test/create a SoC with a CPU):

$ ./litex_setup.py gcc

- Build the target of your board...:

Go to litex-boards/litex_boards/targets and execute the target you want to build.

- ... and/or install Verilator and test LiteX directly on your computer without any FPGA board:

On Linux (Ubuntu):

$ sudo apt install libevent-dev libjson-c-dev verilator

$ lxsim --cpu-type=vexriscv

On MacOS:

$ brew install json-c verilator libevent

$ brew cask install tuntap

$ lxsim --cpu-type=vexriscv

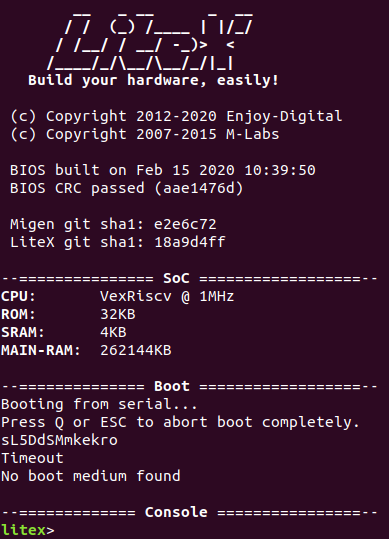

- Run a terminal program on the board's serial port at 115200 8-N-1.

You should get the BIOS prompt like the one below.

Community

LiteX has been initially developed by EnjoyDigital to create custom SoCs/Systems for our clients (and we are still using it for that purpose :)); but over the years a friendly community has grown around LiteX and the ecosystem of cores. Feedbacks and contributions have already greatly improved the project, EnjoyDigital still leads the development but it is now a community project and collaborative projects created around/with LiteX can be found at https://github.com/litex-hub.

Contact

E-mail: florent@enjoy-digital.fr